ESP32-S3日常开发经常用到的信息提取出来放到一篇文档中

一、基本信息

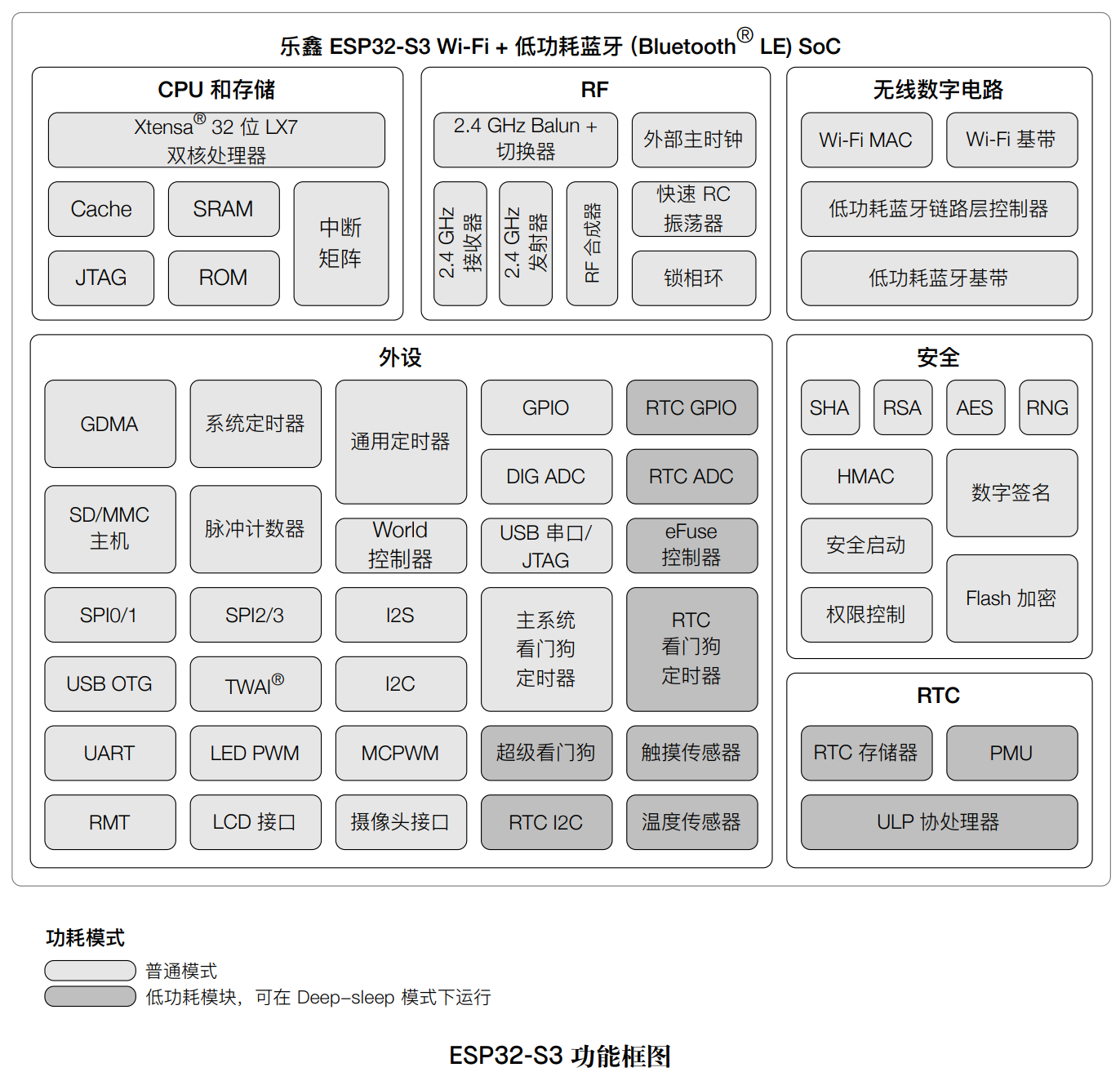

32-bit MCU & 2.4 GHz Wi-Fi & Bluetooth 5 (LE)

Xtensa® 32 位 LX7 双核处理器,主频高达 240 MHz

内置 512 KB SRAM、384 KB ROM 存储空间、RTC SRAM:16 KB

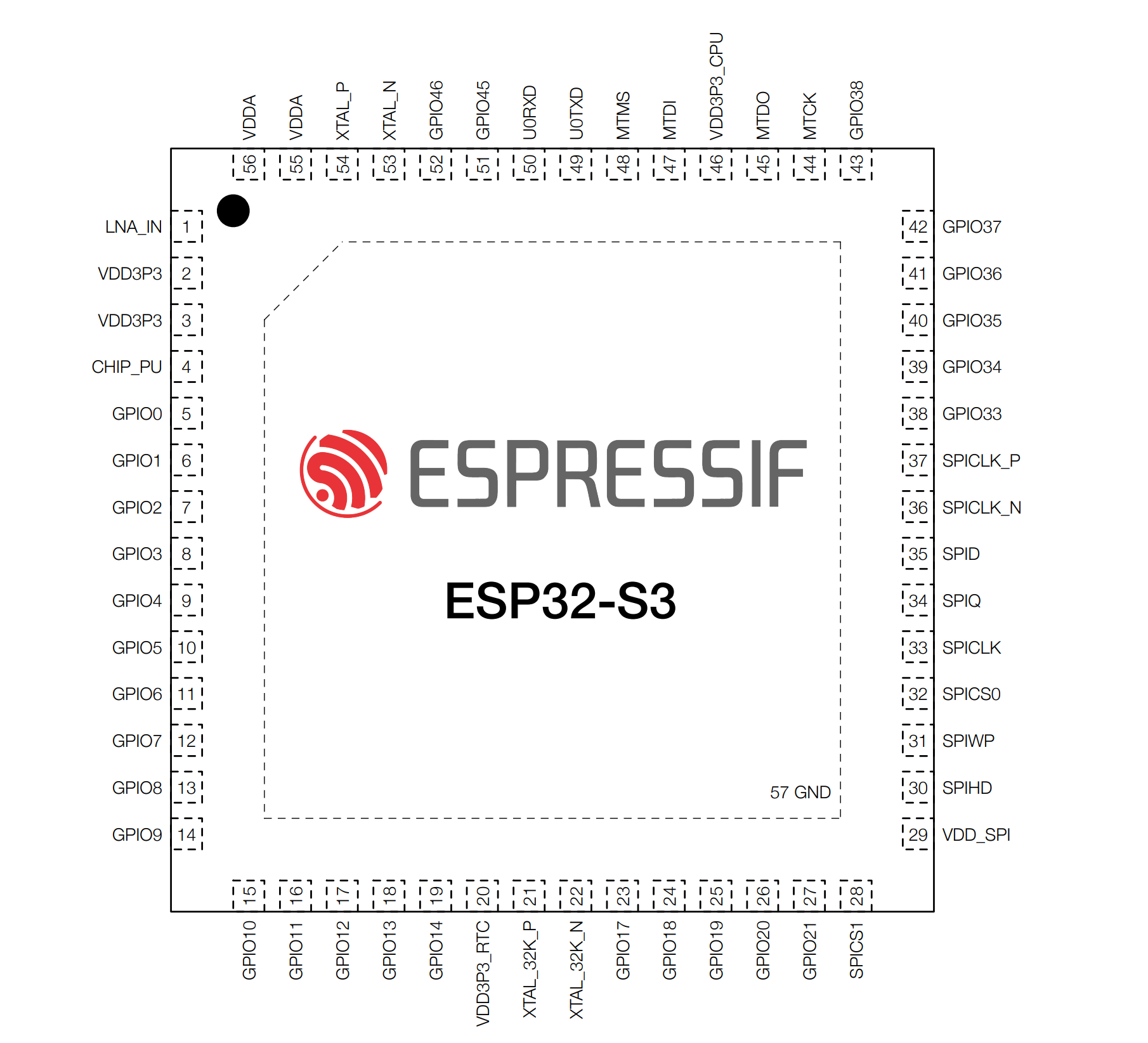

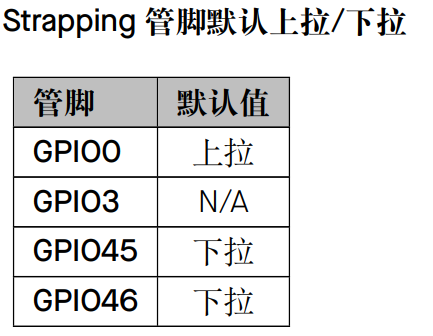

45 个可编程 GPIO、 4 个 strapping 管脚(GPIO0、GPIO3、GPIO45、GPIO46)

* 6 个用于连接封装内 封装内 flash 或 PSRAM

* 7 个用于同时连接封装内 封装内 flash 和 PSRAM

QFN56 (7×7 mm) 封装

二、资源

3 个 UART、2 个 I2C、2 个 I2S

2 个 SPI 接口用于连接 flash 和 RAM

2 个通用 SPI 接口

LCD 接口、DVP 8 位 ~ 16 位摄像头接口

TWAI® 控制器,兼容 ISO11898-1(CAN 规范 2.0)

全速 USB OTG

USB 串口 /JTAG 控制器

SD/MMC 主机接口,具有 2 个卡槽

LED PWM 控制器,多达 8 个通道

2 个电机控制脉宽调制器 (MCPWM)

RMT (TX/RX)、脉冲计数器

2 个 12 位 SAR ADC,多达 20 个通道

内部温度传感器

14 个电容式传感 GPIO

4 个 54 位通用定时器

52 位系统定时器

3 个看门狗定时器

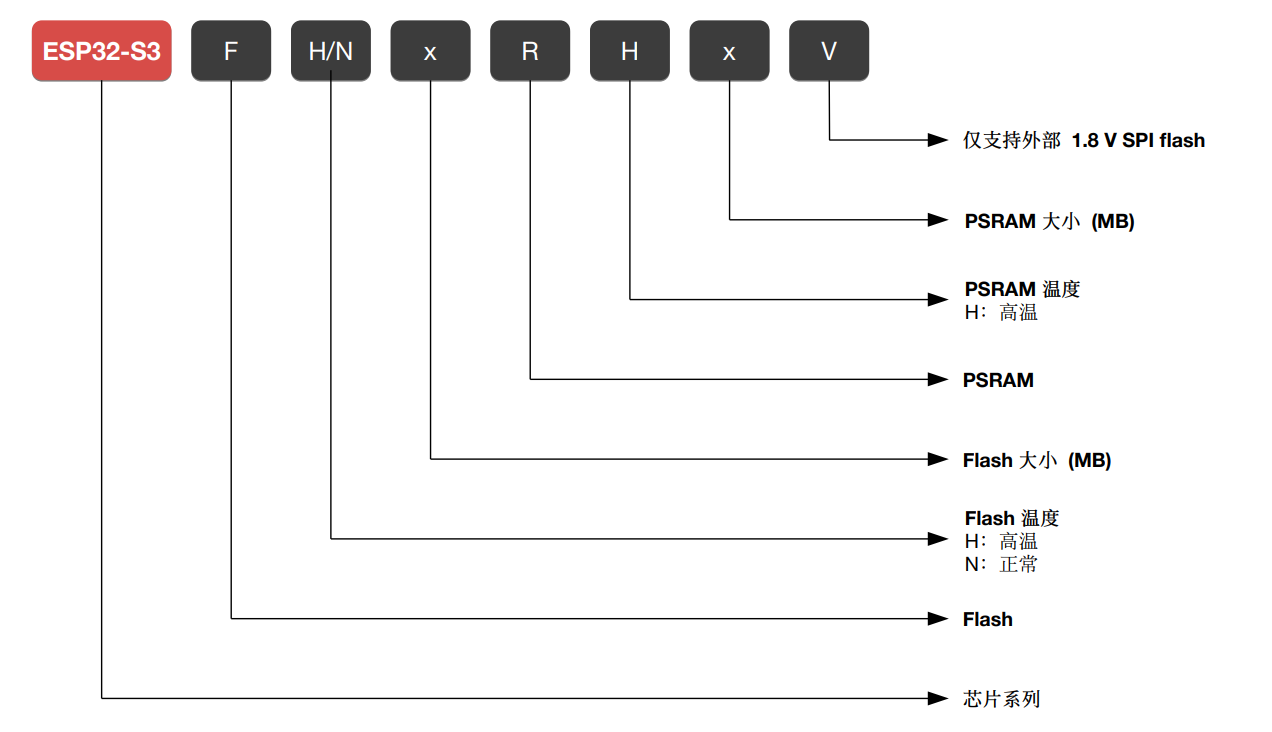

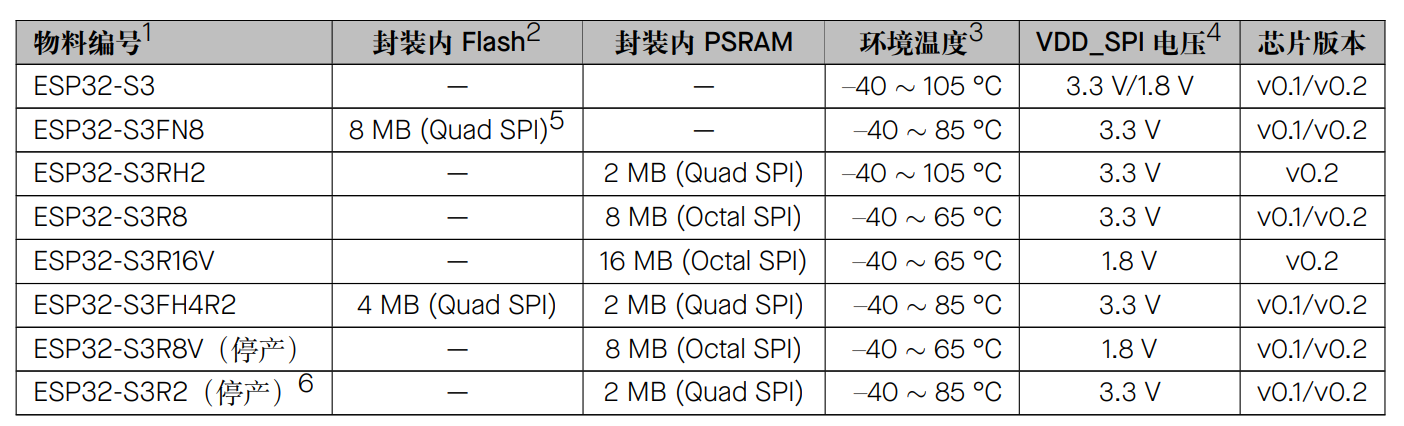

三、命名和型号对比

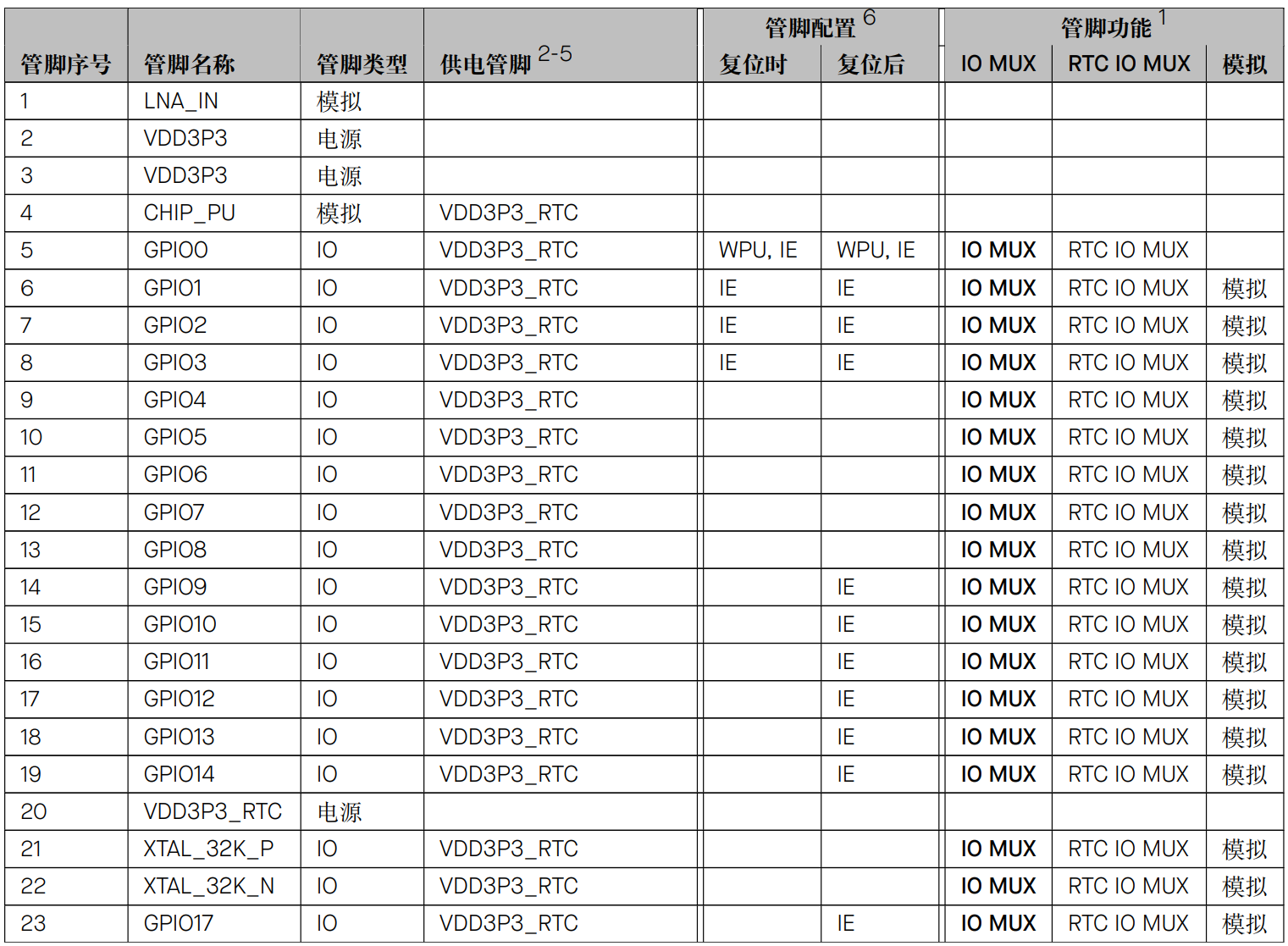

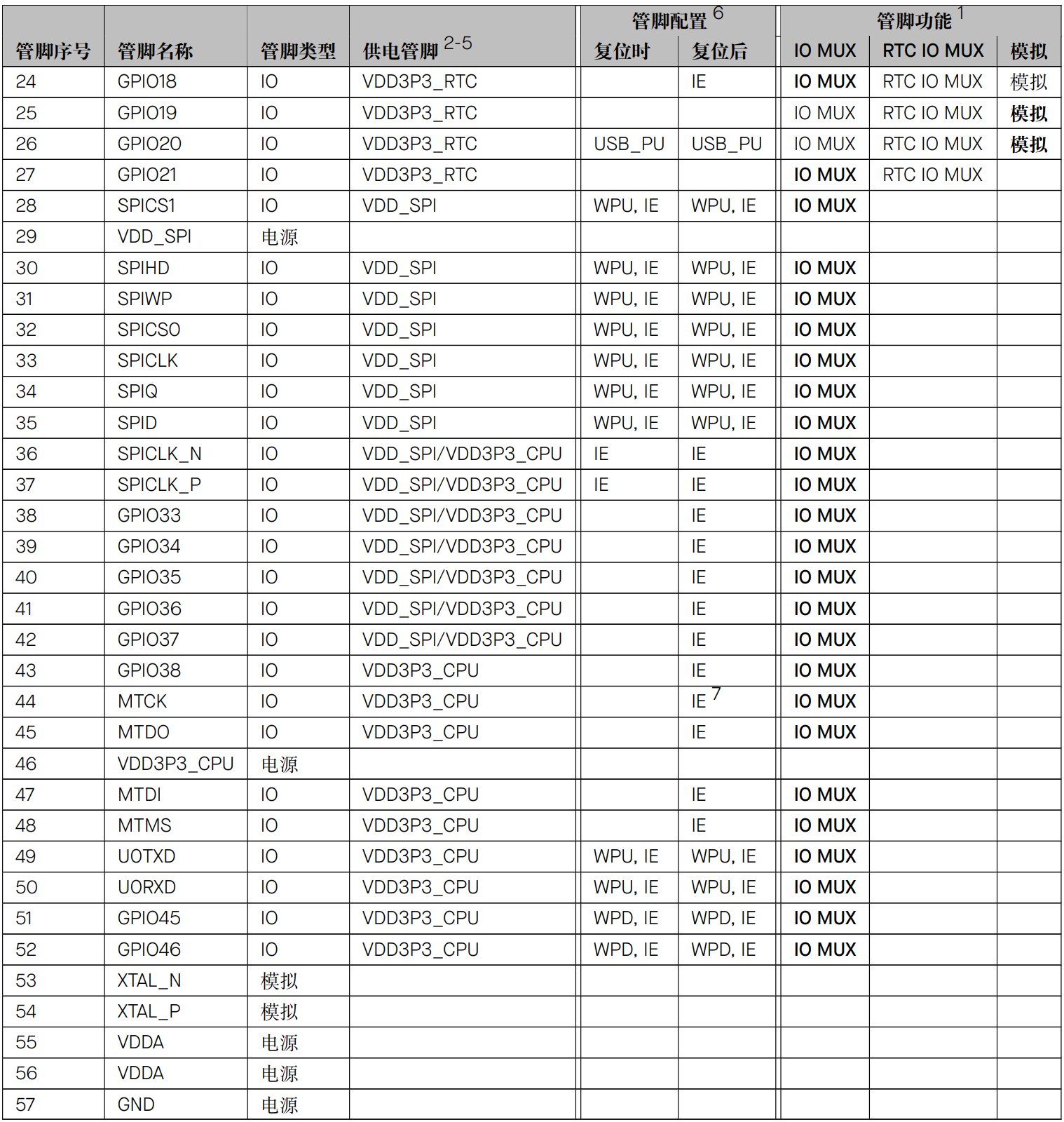

四、管脚

管脚概述

各管脚的默认驱动电流为:

GPIO17 和 GPIO18:10 mA

GPIO19 和 GPIO20:40 mA

其他管脚:20 mA

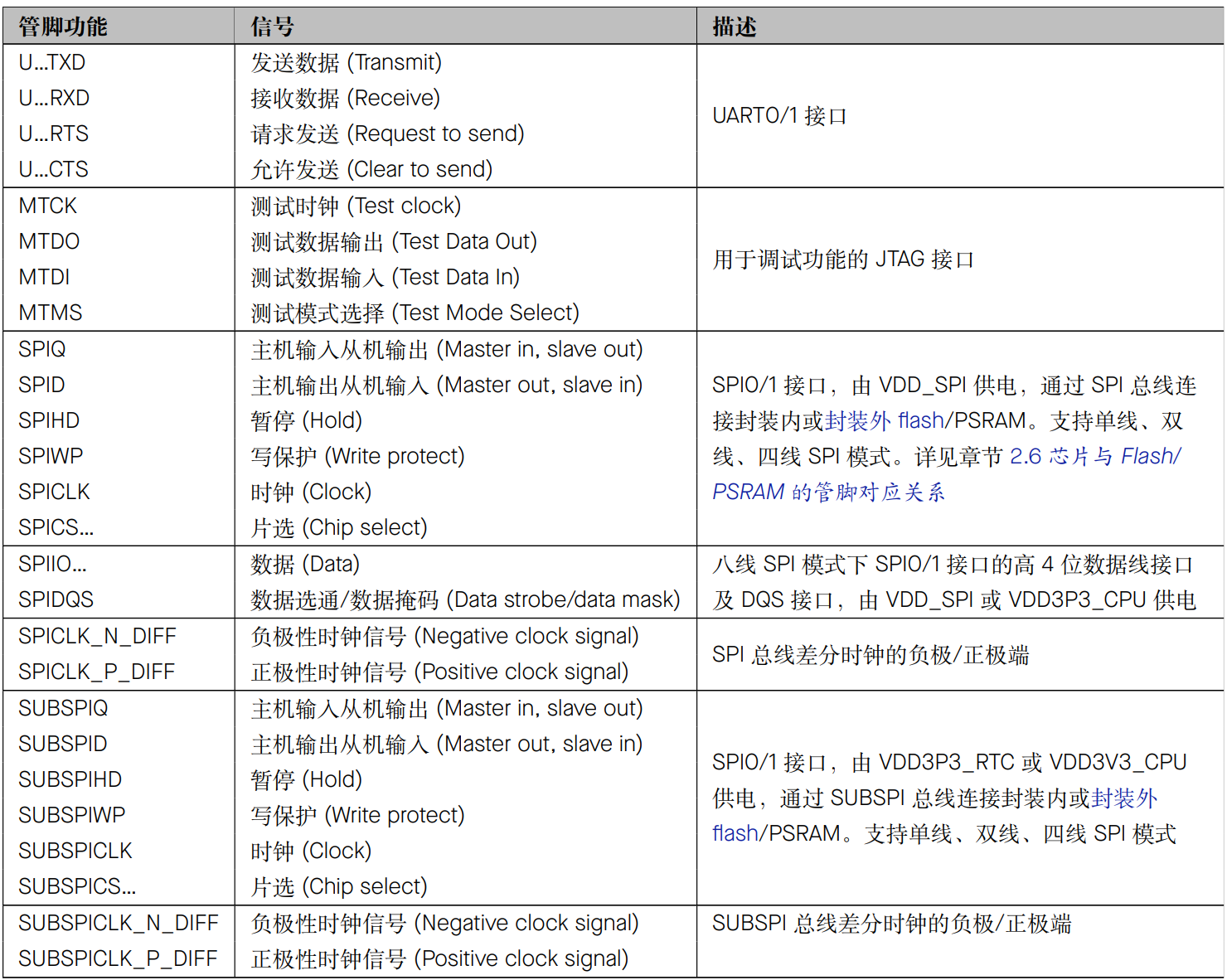

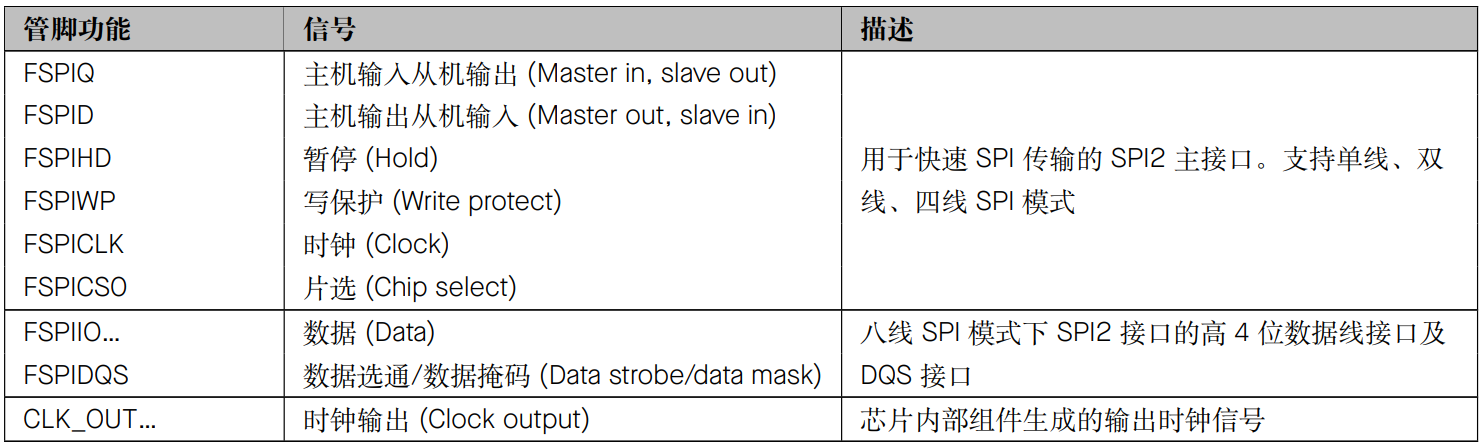

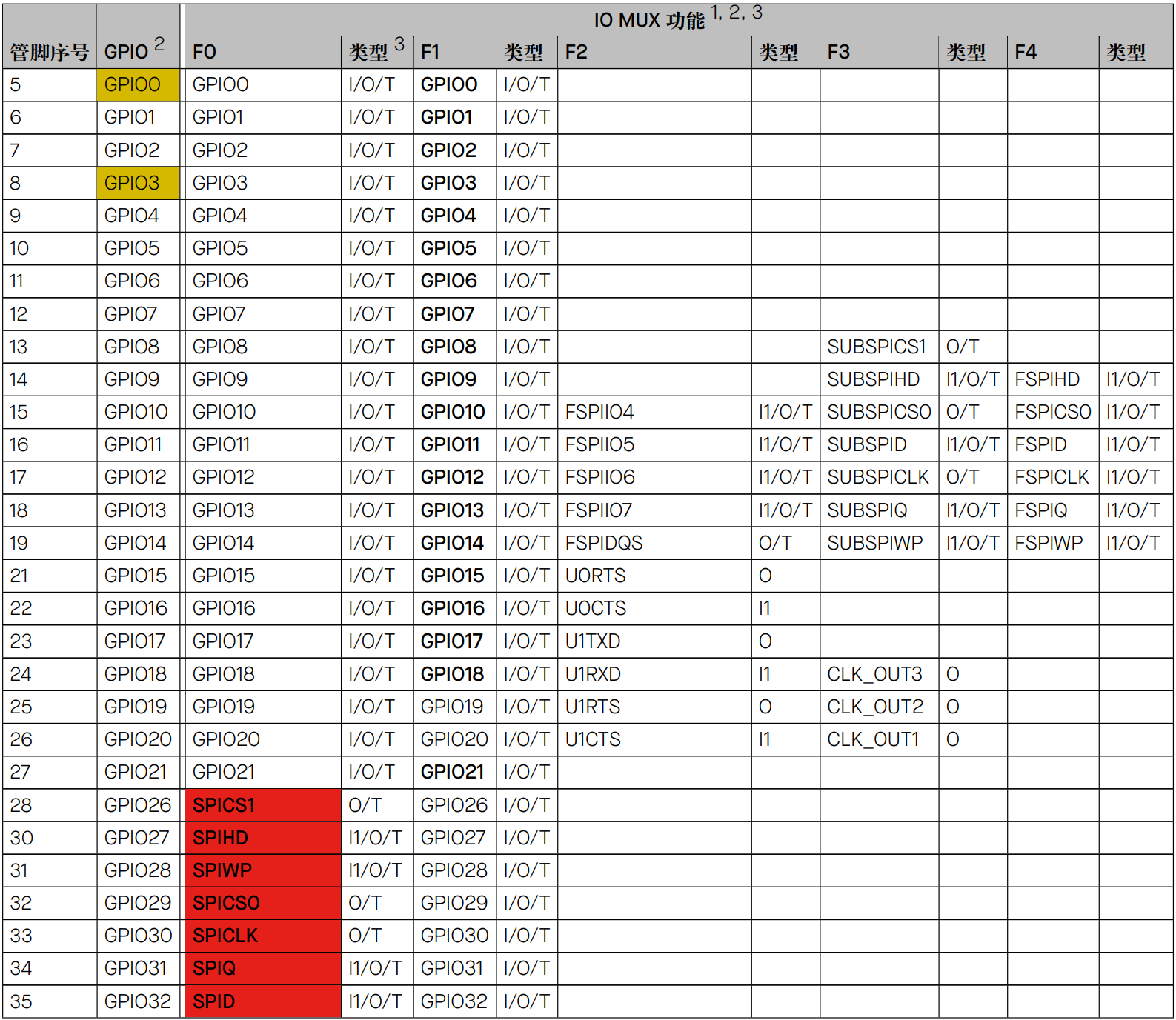

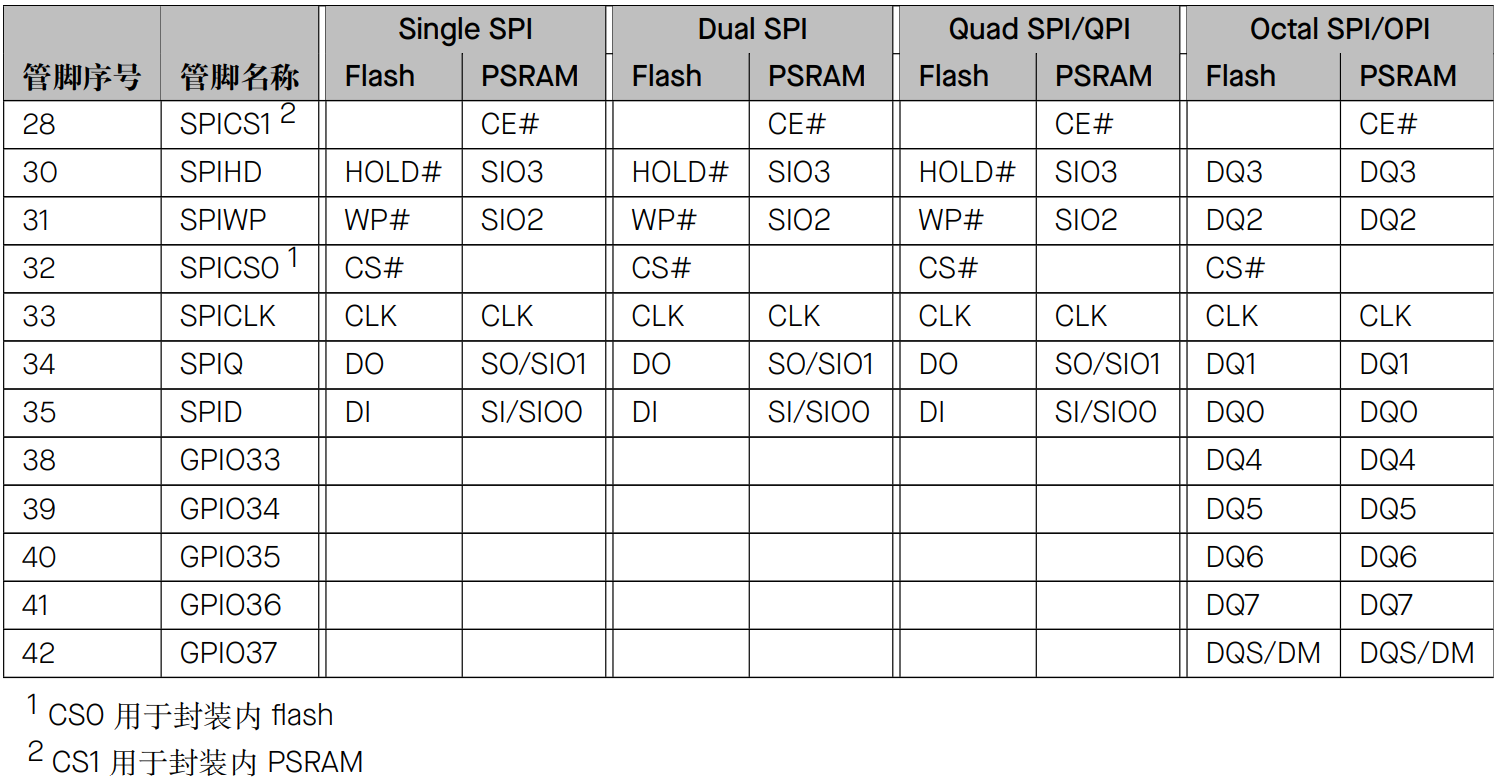

IO MUX 连接的外设信号

IO MUX 功能

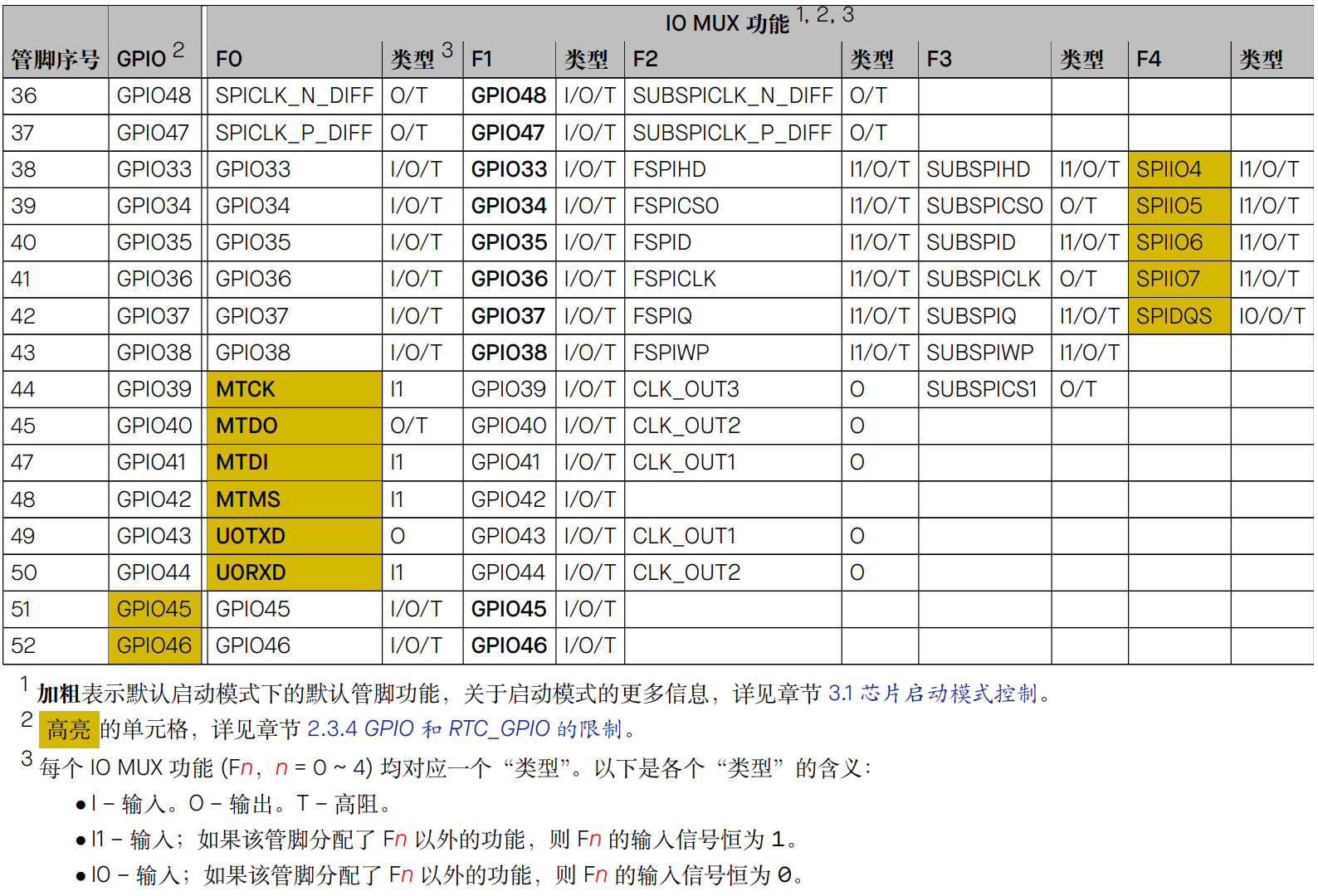

芯片与 flash 或 PSRAM 的管脚对应关系

ESP32-S3 支持以 SPI、Dual SPI、Quad SPI、Octal SPI、QPI、OPI 等接口形式连接 flash 和片外 RAM。 外部 flash 和片外 RAM 可以映射到 CPU 的指令空间、只读数据空间,片外 RAM 还可以映射到 CPU 的数据空 间。外部 flash 和片外 RAM 各可以最大支持 1 GB。ESP32-S3 支持基于 XTS-AES 的硬件加解密功能,从而保护 开发者 flash 和片外 RAM 中的程序和数据。

通过高速缓存,ESP32-S3 一次最多可以同时有:

外部 flash 与片外 RAM 以 64 KB 的块映射到 32 MB 的指令空间。

片外 RAM 以 64 KB 的块映射到 32 MB 的数据空间,支持 8 位、16 位、32 位和 128 位读写。外部 flash 也 可以映射到 32 MB 只读数据空间,仅支持 8 位、16 位、32 位和 128 位读取。

外设管脚分配

可能或冲突的管脚:

GPIO0、GPIO3、GPIO45、GPIO46 :Strapping 管脚

GPIO19、GPIO20 :USB 串口 /JTAG 接口

GPIO39、GPIO40、GPIO41、GPIO42 :JTAG 接口

GPIO43、GPIO44 : UART0 接口

GPIO33、GPIO34、GPIO35、GPIO36、GPIO37 : 八线 SPI 模式下 SPI0/1 接口的高 4 位数据线 接口及 DQS 接口,在不使用八线 SPI 模式连接 flash 或 PSRAM 时可用作 GPIO

GPIO26、GPIO27、GPIO28、GPIO29、GPIO30、GPIO31、GPIO32 :SPI0/1 管脚,已连接封装 内 flash 和 PSRAM,或推荐连接封装外 flash 和 PSRAM

五、芯片 Boot 控制

芯片在上电或硬件复位时,可以通过 Strapping 管脚 和 eFuse 参数 配置如下启动参数,无需微处理器的参与:

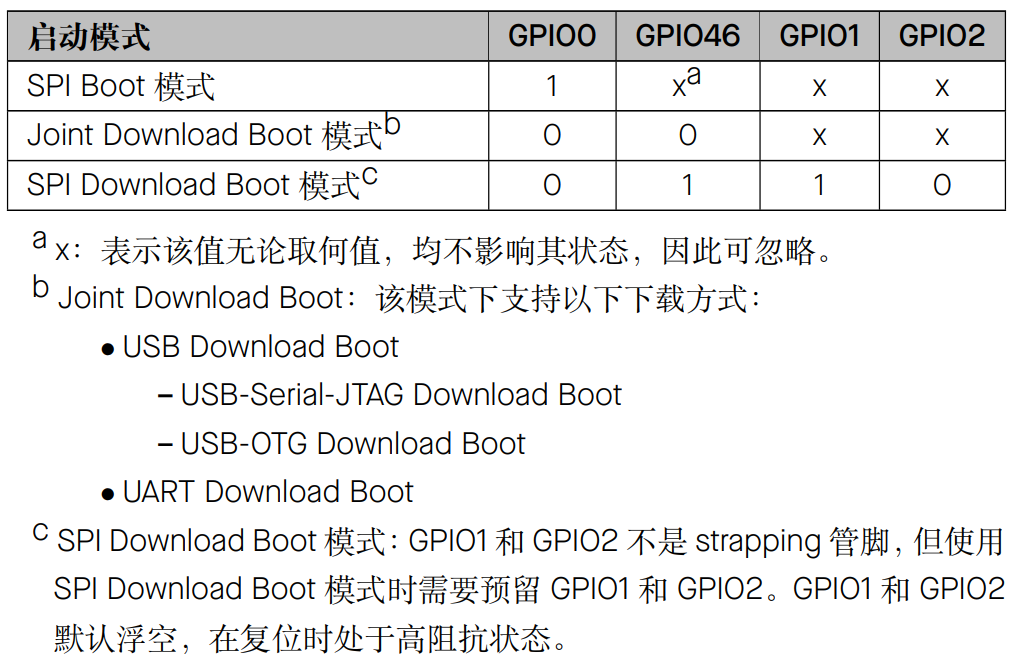

芯片启动模式

Strapping 管脚:GPIO0 和 GPIO46

VDD_SPI 电压

Strapping 管脚:GPIO45

eFuse 参数:EFUSE_VDD_SPI_FORCE 和 EFUSE_VDD_SPI_TIEH

ROM 日志打印

Strapping 管脚:GPIO46

eFuse 参数:EFUSE_UART_PRINT_CONTROL 和 EFUSE_DIS_USB_SERIAL_JTAG_ROM_PRINT

JTAG 信号源

Strapping 管脚:GPIO3

eFuse 参数:EFUSE_DIS_PAD_JTAG、EFUSE_DIS_USB_JTAG 和 EFUSE_STRAP_JTAG_SEL

eFuse 参数的默认值均为 0,也就是说没有烧写过。eFuse 只能烧写一次,一旦烧写为 1,便不能恢复为 0。 有关烧写 eFuse 的信息,请参考 《ESP32-S3 技术参考手册》 > 章节 eFuse 控制器。

GPIO0、GPIO45 和 GPIO46 默认连接内部上拉 / 下拉。如果这些管脚没有外部连接或者连接的外部线路处于高 阻抗状态,内部弱上拉 / 下拉将决定这几个管脚输入电平的默认值,

如需改变 Strapping 管脚的默认值,用户可以应用外部下拉 / 上拉电阻,或者应用主机 MCU 的 GPIO 来控制 ESP32-S3 上电复位时的 Strapping 管脚电平。复位释放后,Strapping 管脚和普通管脚功能相同。

Boot 模式控制

ROM 日志打印控制

系统启动过程中,ROM 代码日志可打印至:

(默认)UART0 和 USB 串口 /JTAG 控制器

USB 串口 /JTAG 控制器

UART0

通过配置寄存器和 eFuse 可分别关闭 UART 和 USB 串口 /JTAG 控制器的 ROM 代码日志打印功能。详细信息请 参考 《ESP32-S3 技术参考手册》 > 章节 芯片 Boot 控制